What is FPGA-Based System Design?

Definition & Core Concepts

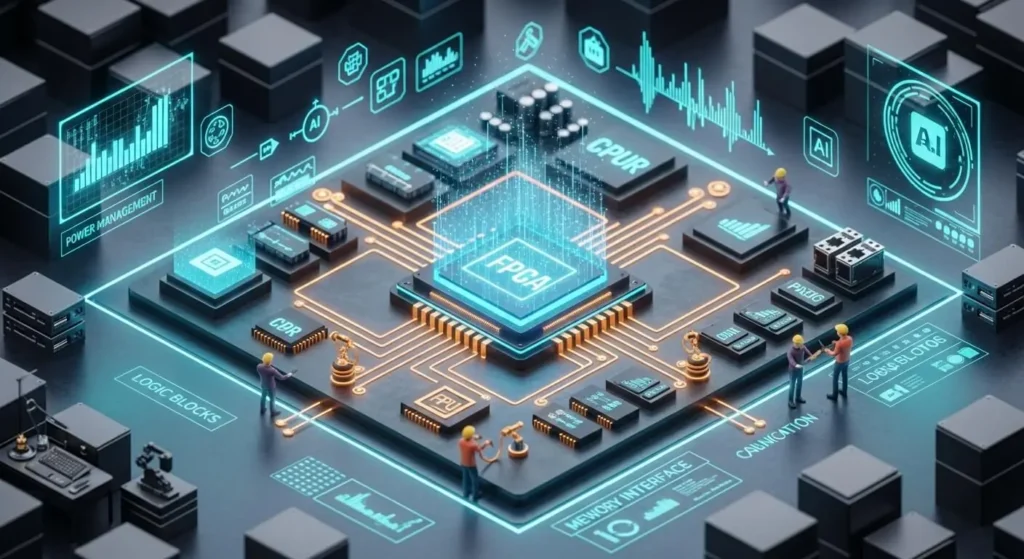

An FPGA (Field-Programmable Gate Array) is a semiconductor device that can be programmed (or configured) after manufacturing to implement custom logic, interconnects, and I/O structures. Unlike fixed ASICs, you can re-configure FPGAs, iterate faster, and adapt to changing requirements.

In an FPGA-based system design, the FPGA often serves as a central component in the hardware architecture — e.g., as a custom accelerator, a SoC fabric, or logic accelerator intermixed with CPUs/GPUs. You are designing the system in which the FPGA coexists with processors, memory, I/O, software stacks, and board infrastructure.

Why Choosing FPGA Makes Sense

Here are some advantages of choosing FPGA-based systems:

- Flexibility & re-configurability – You can iterate hardware logic without re-fabricating silicon. AJBAS+1

- Performance & parallelism – FPGAs can exploit fine-grained parallelism and pipelined logic, delivering high throughput and low latency.

- Time-to-market advantage – Because there’s no full mask-set ASIC turn, design cycles can be faster for many prototyping and low-volume use-cases. EECG Toronto+1

- Heterogeneous computing enablement – FPGAs integrate into systems with CPUs/GPUs to offload tasks (e.g., DSP, ML inference, encryption) and provide domain-specific acceleration. Trieste Arts Dept.

But there are trade-offs: as pointed out, FPGAs typically have higher area, power and cost overhead compared to ASICs or CPUs for the same task. EECG Toronto+1

Key Design Considerations for FPGA-Based Systems

Architectural Choices

When designing an FPGA-based system, consider:

Partitioning Between Hardware & Software

Deciding which functions go into FPGA logic vs software/firmware is critical. E.g., compute-intensive kernels (image processing, DSP, encryption) might go in logic, while control flow, user interface, OS tasks stay on CPU.

Interconnect & Memory Architecture

The performance of your system hinges on how you connect FPGA logic to memory and I/O. High bandwidth, low latency memory access, and efficient bus/interconnect are key. Research shows that routing and interconnect fabrics dominate trade-offs in FPGA architecture (area, speed, power). EECG Toronto+1

Power & Thermal Budget

While FPGAs offer flexibility, they tend to consume more dynamic power and may require careful thermal design. Designers must evaluate power/area efficiency when comparing to ASICs or GPUs. EECG Toronto+1

Toolflow and Design Productivity

Using tools like high-level synthesis (HLS), IP integration frameworks, and design automation can greatly accelerate development. For instance, frameworks enable software engineers (with less HDL expertise) to design FPGA-based systems. arXiv+1

Recent Trends & Emerging Areas

Heterogeneous Computing Clusters

Modern research emphasizes FPGA-based heterogeneous clusters — combining CPUs, GPUs and FPGAs — especially for high-performance and power-efficient computing. Trieste Arts Dept.

Edge Inference & AI Acceleration

Deploying deep-neural-network (DNN) models on FPGA at the edge is growing: FPGAs provide a balance of performance and power for inference tasks. arXiv+1

Domain-Specific Frameworks

Frameworks tailored for FPGA system design (e.g., for application programmers, not just hardware engineers) are gaining traction. arXiv

A Step-by-Step Design Workflow for FPGA Systems

From Concept to Deployment

Here’s a typical workflow you might adopt:

- Requirement capture & partitioning – Define system requirements (throughput, latency, power, cost) and partition tasks between FPGA logic and software.

- Architecture design – Decide on FPGA device family, board layout, I/O, memory interfaces, interconnect, and software stack.

- RTL/HLS development – Write or generate HDL (or use HLS) for the logic blocks, design IPs, validate using simulation.

- Integration & verification – Integrate FPGA logic with software, processors, memories, and run functional simulation, hardware emulation.

- Synthesis, place-&-route & timing closure – Use vendor tools to implement on the FPGA, optimize for timing, area, power.

- Board bring-up & system validation – Load design onto board, test with real I/O, run performance benchmarks and reliability tests.

- Deployment & maintenance – If re-configurability is required, manage FPGA bitstreams, updates, version control.

Best Practices & Tips

- Use IP cores from vendors or open-source libraries when appropriate to accelerate development.

- Adopt modular design: partition logic into reusable blocks, use clear interfaces.

- Optimize for dataflow: design logic to minimize memory bottlenecks and maximize streaming.

- Early power modelling: estimate power during architecture phase to avoid later surprises.

- Plan for future updates: FPGA systems excel when you anticipate change (e.g., algorithm updates) — use reconfigurable logic wisely.

- Use verification early and frequently: emulate critical paths, use hardware-in-the-loop if possible.

Applications Where FPGA-Based Systems Shine

Use-Cases

- High-speed signal & image processing (radar, lidar, medical imaging)

- Encryption & secure communications — hardware logic for AES, RSA, etc. IJIREEICE

- AI/ML acceleration at the edge — deploy DNN inference with power constraints.

- HPC and data-centre acceleration — FPGAs in heterogeneous clusters to offload specific kernels. Trieste Arts Dept.

- Embedded SoC or custom logic solutions — e.g., combining soft-cores, logic blocks and custom IP on FPGA.

Challenges & Limitations

What to Watch Out For

- Higher cost per unit (for large volumes) compared to ASICs.

- Design complexity – requires knowledge of hardware design, timing closure, FPGA-specific optimisation.

- Toolchain maturity & learning curve – engineering teams may need to upskill.

- Power/area inefficiency relative to ASICs in some cases. EECG Toronto

- Longer compile and iteration times – especially for large FPGAs, place/route can be time-consuming.